# Welcome To The RISC-V Revolution!

Moscow, Russia May 20, 2019

Feb 2019 USA II Mar & May 2019 China II May 2019 Europe II Jun 2019 Asia-Pacific II Jun 2019 Australia Jun 2019 China II Jul 2019 Pakistan II Aug 2019 India II Aug 2019 USA II Sep 2019 Middle East II Oct 2019 China Nov 2019 Mexico II Nov 2019 South America

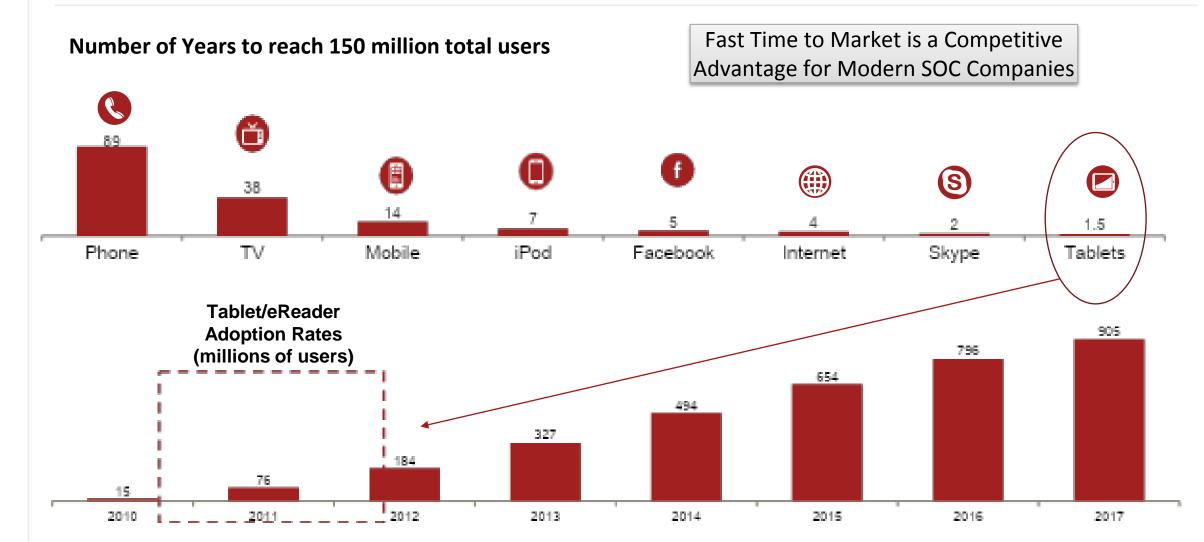

## New Multi-Billion-Dollar Markets are Being Created in Quarters, Not Decades

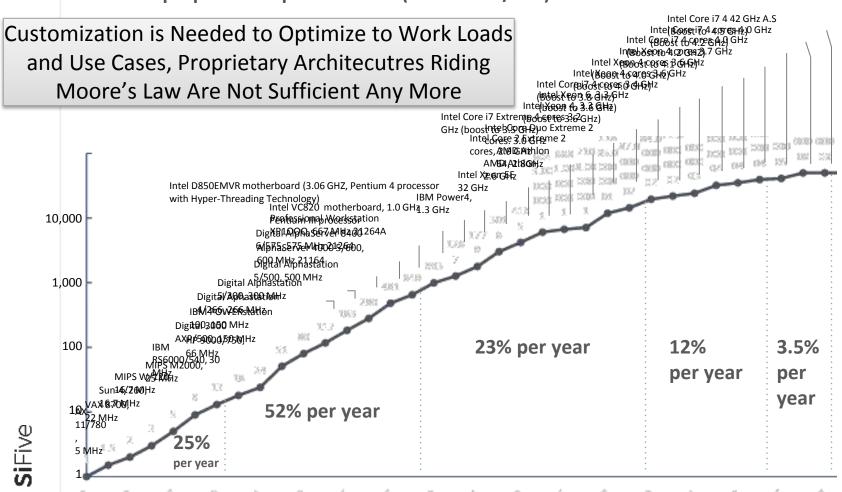

## The Benefits of Moore's Law are Slowing; Moore's Law is Financially Failing

#### Moore's Law Has Stalled

**General-purpose CPU performance (vs. VAX-11/780)**

## Time for a Paradigm Shift

**Customization** is the only way to get performance

One-Chip-Fits-All **no longer applies**

**Innovation** is desperately needed to meet the needs of new applications running on billions of devices

## Agenda

| 09:00 - 10:00 | Registration                                                                                                           |

|---------------|------------------------------------------------------------------------------------------------------------------------|

| 10:00 - 10:10 | Welcome and Introduction, by Jaspi Sandhu, VP of Sales, SiFive                                                         |

| 10:10 - 10:50 | RISC-V History and State of the Union, by Krste Asanovic, Chairman of RISC-V Foundation                                |

| 10:50 – 11:10 | Professional Development Tools for RISC-V, by Felipe Torrezan, FAE, IAR Systems                                        |

| 11:10 – 11:40 | Keynote: Leading Semiconductor Design Revolution, by Krste Asanovic, Co-Founder and Chief Architect, SiFive            |

| 11:40 – 12:00 | Break                                                                                                                  |

| 12:00 – 12:20 | SCRx Family of the RISC-V Compatible CPU IP, by Pavel Khabarov, Lead Engineer, Syntacore                               |

| 12:20 – 12:40 | Analytics, Tracing and Debugging Tools for the SoC Level for Projects Based on RISC-V, by Rupert Baines, CEO, UltraSoC |

| 12:40 - 13:00 | MicroTESK for RISC-V: Test Coverage Generation and Binary Code Analysis, by Alexander Kamkin, Lead Researcher, ISP RAS |

| 13:00 – 14:00 | Lunch and Demos                                                                                                        |

| 14:00 – 14:20 | RISC-V Core IP for Target Vertical Markets, by Jahoor Vohra, Sr. FAE, SiFive                                           |

| 14:20 - 14:40 | RISC-V Software Ecosystem Overview, by Syntacore                                                                       |

| 14:40 – 15:00 | Freedom Revolution: Customizable RISC-V AI SoC Platform, by Krste Asanovic, Co-Founder and Chief Architect, SiFive     |

| 15:00 – 15:30 | Keynote: Development of RISC-V in Russia, by Alexander Redkin, CEO, Syntacore                                          |

| 15:30 – 15:50 | Break                                                                                                                  |

| 15:50 – 16:15 | Tutorial: SiFive Core Designer, by Jahoor Vohra, Sr. FAE, SiFive                                                       |

| 16:15 – 16:40 | Tutorial: Using SCR1 – Open RISC-V MCU Syntacore Kernel, Ekaterina Berezina, Senior HW Engineer, Syntacore             |

| 16:40 - 16:50 | Video: Design Your Own CPU!!                                                                                           |

| 16:50 - 17:00 | Closing Remarks, by Alexander Redkin, Executive Director, Syntacore                                                    |

| 17:00 – 18:00 | Networking/Demos                                                                                                       |

|               |                                                                                                                        |

## Special thanks to our sponsors

## **HOSTs**

#### **PARTNERS**

## Silicon verified. Market proven.

The most advanced configurable core IP and silicon solutions from the inventors of RISC-V.

Microcontrollers - Embedded - Linux - Multicore

- Networking Storage Computing Al

- Industrial IoT Consumer Automotive

www.sifive.com