SiFive Core Designer

From Custom CPU to Hello World in 30 Minutes

# Silicon at the speed of speed of software. Design RISC-V CPUs in an hour. Get custom SoCs in weeks, not months. Impossible? Not anymore.

**Start Designing**

#### **SiFive Core Designer**

#### Your interface to SiFive RISC-V Core IP

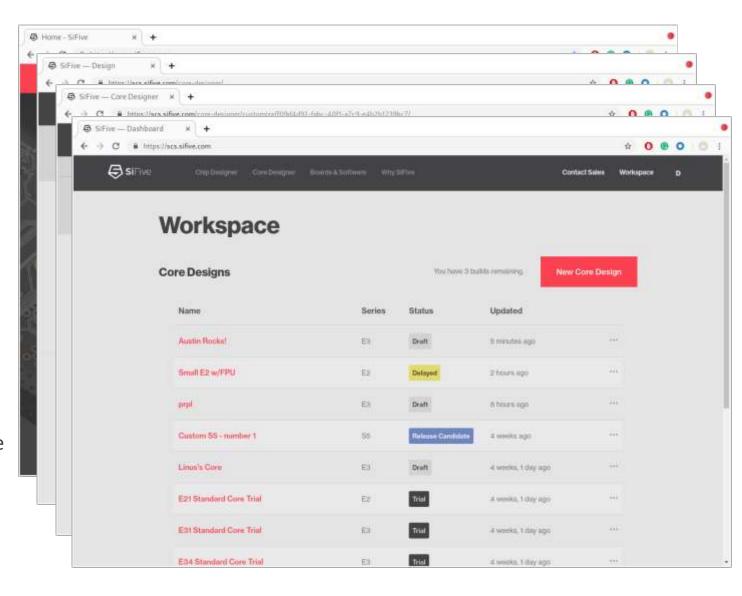

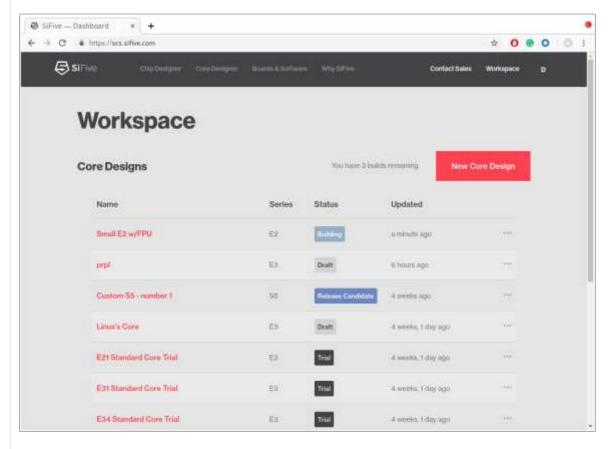

- All SiFive Core IP is configured and delivered via the SiFive Core Designer Web Portal

- Simple, Easy to Use, Web Interface

- **Release Candidates** are generated with click of a button and available from the Workspace

- Release Candidates contain

- RTL matching the configuration, including a testbench, and other collateral needed to realize the design

- Documentation specific to the design

- Customized bare-metal BSP for easy integration into SiFive's SDKs

- **FPGA** bitstreams for common FPGA development boards for easy software benchmarking of the RC

3

#### In-house IP: SiFive RISC-V Core IP Product Offering

**E**Cores

**32-bit embedded cores** MCU, edge computing, AI, IoT

S Cores

**64-bit embedded cores** Storage, AR/VR, machine learning

**U** Cores

**64-bit application cores** Linux, datacenter, network baseband

#### 7 Series

Highest performance: 8-stage, dual-issue superscalar pipeline

#### **E7 Series**

- > E76-MC Compare to Cortex-M7

Quad-core 32-bit embedded processor

- > E76 Compare to Cortex-M7 > S76

High performance 32-bit embedded core High-

#### **S7 Series**

- > S76-MC No 64-bit Cortex equivalent Quad-core 64-bit embedded processor

- > \$76 No 64-bit Cortex equivalent > U74

High-performance 64-bit embedded core High

#### **U7 Series**

- > U74-MC Compare to Cortex-A55 MP4

Multicore: four U74 cores and one S76 core

- > U74 Compare to Cortex-A55 High performance Linux-capable processor

#### 3/5 Series

#### Efficient performance:

5-6-stage, singleissue pipeline

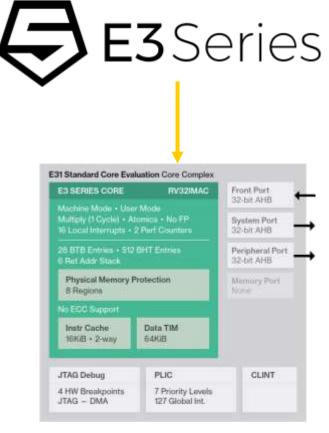

#### E3 Series

- > E34 Compare to Cortex-R5F E31 features + single-precision floating point

- > E31 Compare to Cortex-R5

Balanced performance and efficiency

#### S5 Series

- > **S54** No 64-bit Cortex equivalent S51 features + single-precision floating point

- > S51 No 64-bit Cortex equivalent Low-power 64-bit MCU core

#### **U5 Series**

- > U54-MC Compare to Cortex-A53

Multicore application processor with four U54

cores and one S76 core

- > **U54** Compare to Cortex-A53 Linux-capable application processor

#### 2 Series

#### Power & area optimized:

2-3-stage, singleissue pipeline

#### **E2 Series**

- > E24 Compare to Cortex-M4F E21 + single-precision floating point

- > E21 Compare to Cortex-M4

E20 + User Mode, Atomics, Multiply, TIM

- **E20** Compare to Cortex-M0+ Our smallest, most efficient core

#### S2 Series

> S21 No 64-bit Cortex equivalent Area-efficient 64-bit MCU core

#### From Custom CPU to Hello World in 30 minutes

#### Step 1

Configure a custom SiFive RISC-V Core using SiFive Core Designer

#### Step 2

Use the FPGA bitstream from Step 1 to program a Digilent Arty FPGA board with the configured CPU

#### Step 3

Use Freedom Studio and the SiFive SDK to program and run Hello World

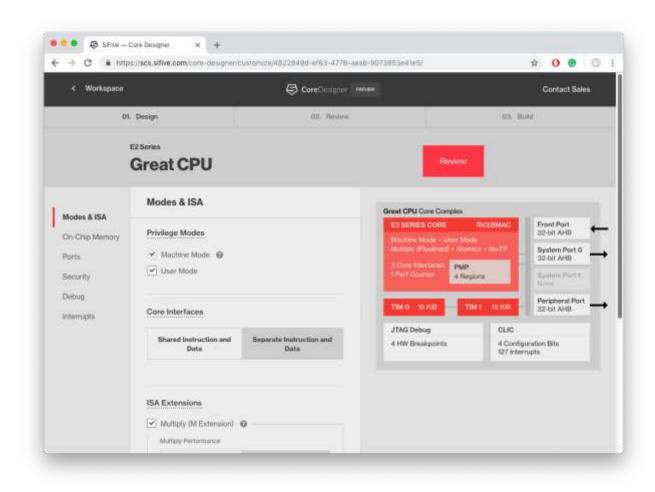

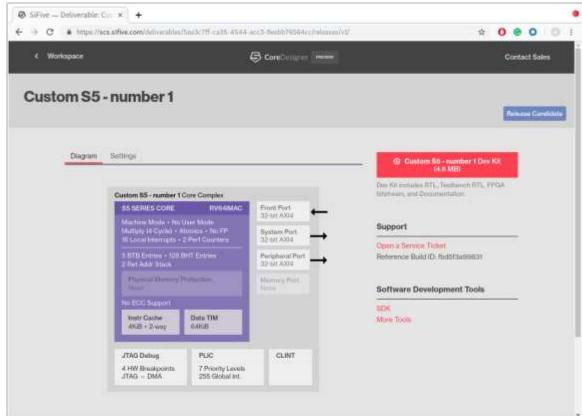

# Step 1 - Configure the Core using SiFive Core Designer

#### https://www.sifive.com/core-designer

# Vastly customizable core IP.

Get best-in-class core IP developed by the inventors of RISC-V and customize it to your exact specifications.

Design Core

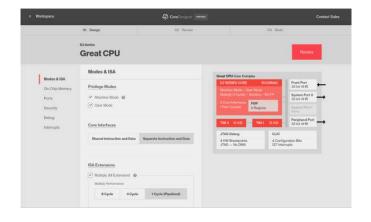

#### **Configure a SiFive RISC-V CPU**

#### **SiFive Core Designer**

#### Web Interface to Configure SiFive Core IP

No Complex EDA tools or scripting languages to learn

#### What is configurable

ISA, Performance levels, Modes, Ports, Interrupts, Security, Debug, and much more!

#### What is the output

Verilog RTL and supporting collateral, an FPGA bitstream, software, and documentation

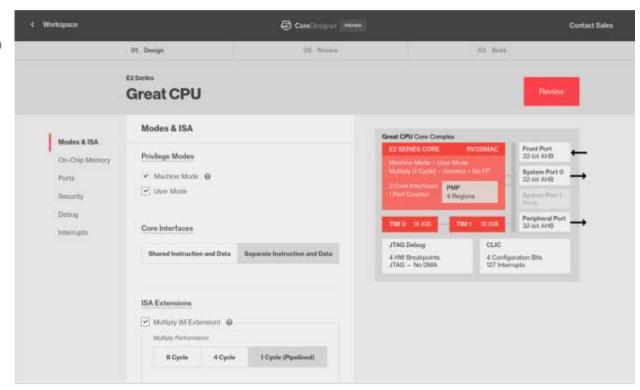

#### Core Designer UI Walkthrough

### Go to the SiFive website and click "Start Designing"

https://www.sifive.com/

#### Choose a Core Series to start from

- Start from a pre-configured Standard Core

- Or start from scratch

#### Name the Design and Start Clicking!

Change performance levels, memory maps, Privilege modes, Instructions Sets, Security, Debug, etc...

#### Click Review and then Build

Launches SiFive's cloud based infrastructure to render and verify the design

#### **Download from your SiFive Workspace**

#### **Too Many Choices? Start with a Standard Core**

E31 Standard Core Definition

FE310 Silicon

Standard Core RTL and FPGA Evaluations are Available with a clickthrough License

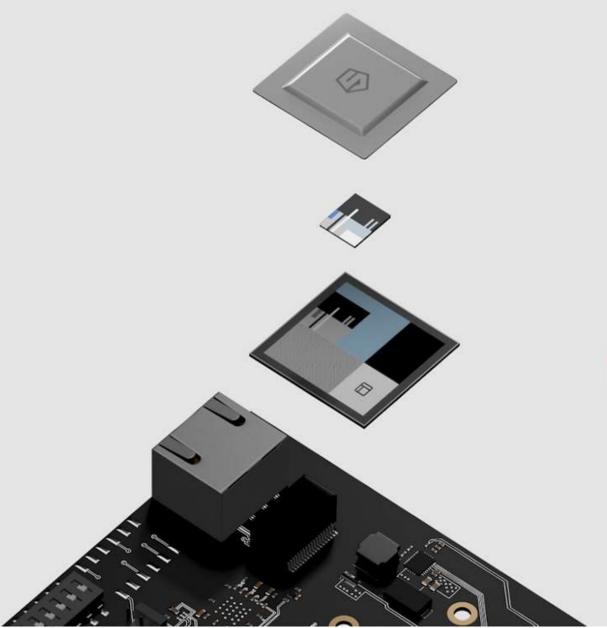

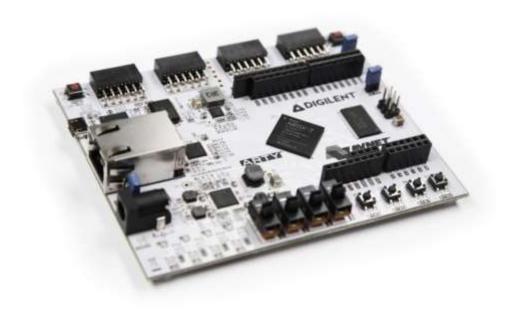

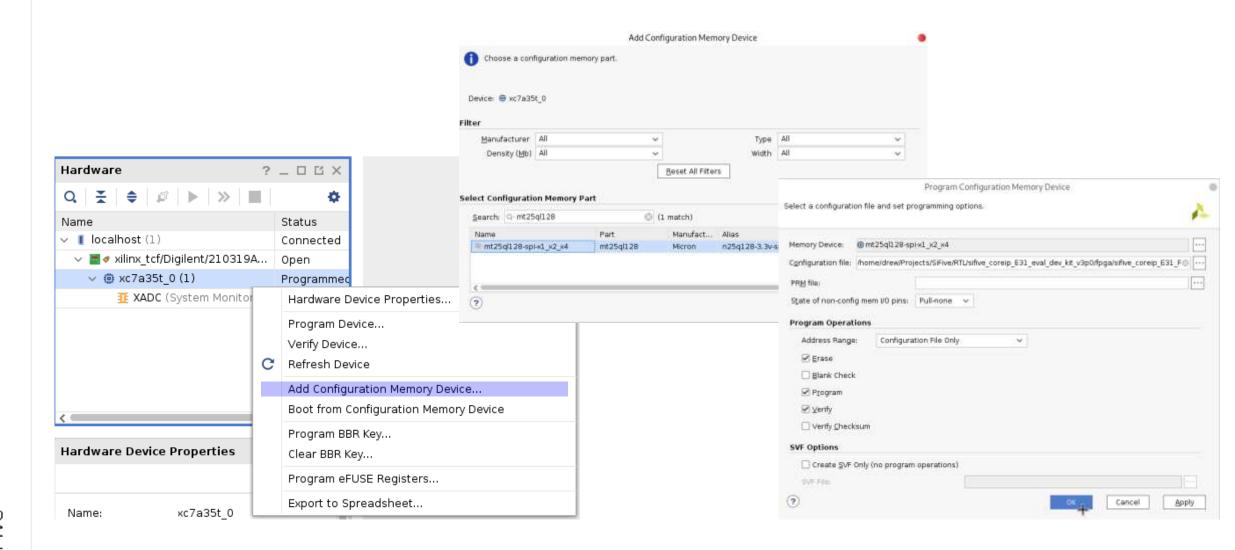

## **Step 2 - Download the Deliverables and Program the FPGA**

#### Download the Deliverables from your SCD Workspace

#### Deploy the bitstream to the FPGA

1. Purchase a Digilent Arty

https://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/

1. Download Xilinx Vivado 2018.3 (Warning, HUGE 19GB)

https://www.xilinx.com/products/design-tools/vivado.html

1. Open Vivado's Hardware Manager Tool

#### Deploy the bitstream to the FPGA In Pictures

# Coming Soon The ability to flash Arty boards directly from Freedom Studio

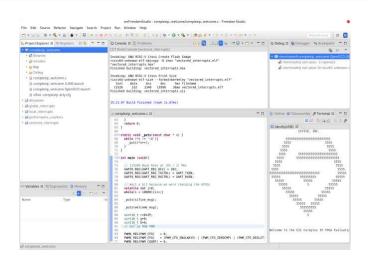

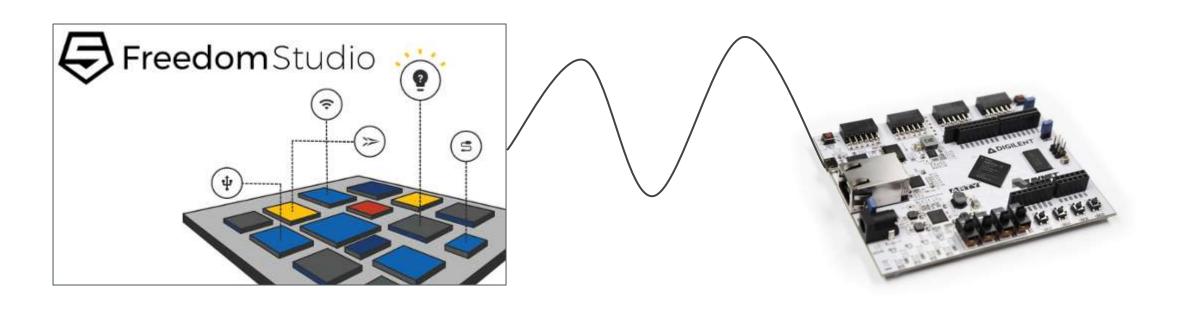

## Step 3 - Hello World!

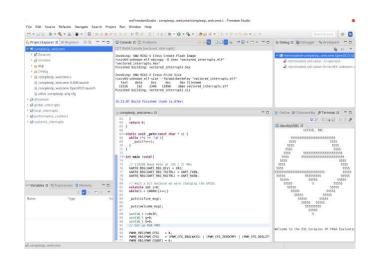

#### **Download Freedom Studio**

- Freedom Studio is an Eclipse based IDE with

- pre-built GCC and OpenOCD

- Bundled examples for SiFive targets

- Download Freedom Studio https://www.sifive.com/boards

- Unzip to the desired installation directory

- Or... Skip the IDE

- Download pre-built binaries of GCC and OpenOCD from the same webpage

- Use Freedom-E-SDK to build and debug your software using a makefile CLI based flow <a href="https://github.com/sifive/freedom-e-sdk">https://github.com/sifive/freedom-e-sdk</a>

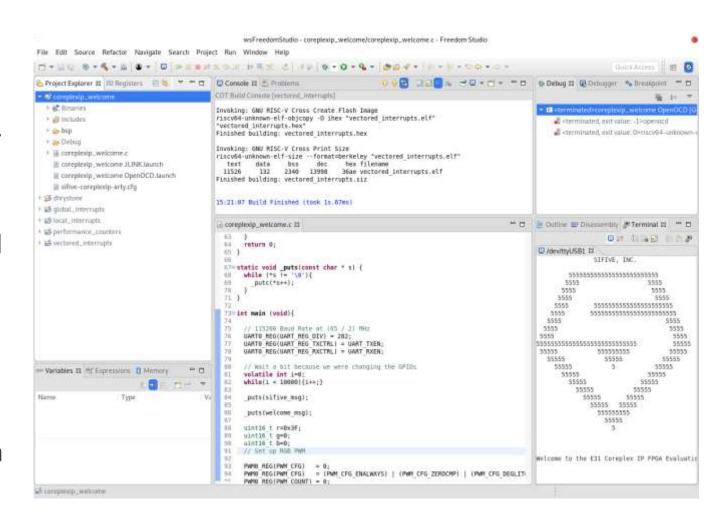

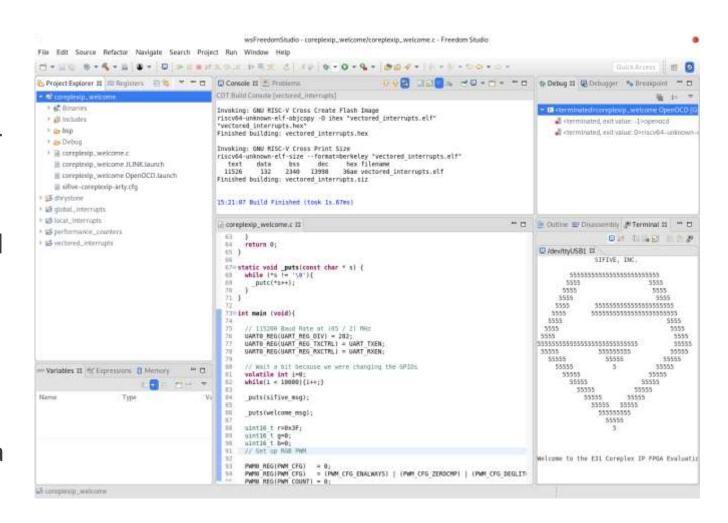

#### **Build and Run the Software**

- File Import DevKit Examples -Browse

- Select the zip that matches your core

- Select the desired examples and click Finish

- Control-B will build the entire workspace

- Run Debug OpenOCD starts a JTAG Debug Session and Loads the program

#### **Build and Run the Software (Change to New Flow)**

- File Import DevKit Examples -Browse

- Select the zip that matches your core

- Select the desired examples and click Finish

- Control-B will build the entire workspace

- Run Debug OpenOCD starts a JTAG Debug Session and Loads the program

#### **Demo - From Custom CPU to Hello World in 30 minutes**

#### Step 1

Configure a custom SiFive RISC-V Core using SiFive Core Designer

#### Step 2

Use the FPGA bitstream from Step 1 to program a Digilent Arty FPGA board with the configured CPU

#### Step 3

Use Freedom Studio and the SiFive SDK to program and run Hello World

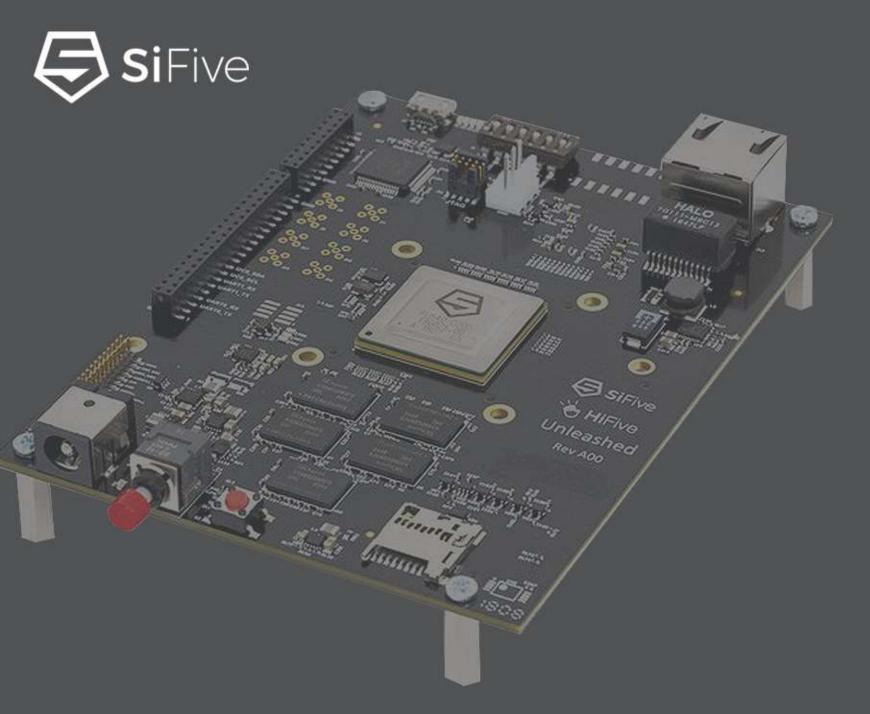

## Silicon verified. Market proven.

The most advanced configurable core IP and silicon solutions from the inventors of RISC-V.

Microcontrollers - Embedded - Linux - Multicore

NetworkingStorageComputingAlIndustrialIoTConsumerAutomotive

www.sifive.com