### RISC-V Core IP for Target Vertical Markets

### SiFive Core IP Embedding Intelligence Everywhere

#### Consumer

AR/VR/Gaming devices

Smart Home

Imaging/Wearables

#### Storage/Networking/5G

SSD, SAN, NAS

Base Stations, Small cells, APs

Switches, Smart NICs, Offload cards

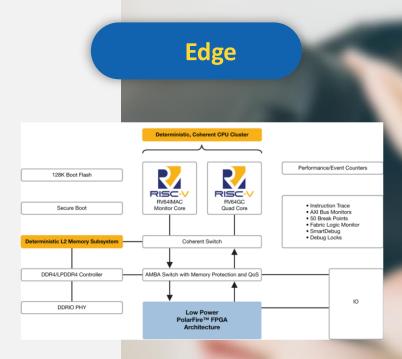

#### **ML/Edge**

Sensor Hubs, Gateways

Autonomous machines

IoT devices

**64-bit Application Processors**

**64-bit Embedded Processors**

32-bit Embedded Processors

**Embedding Intelligence from** the Edge to the Cloud

## SiFive Core IP 2 series:

SiFive's **smallest** and most **efficient** RISC-V processor IP

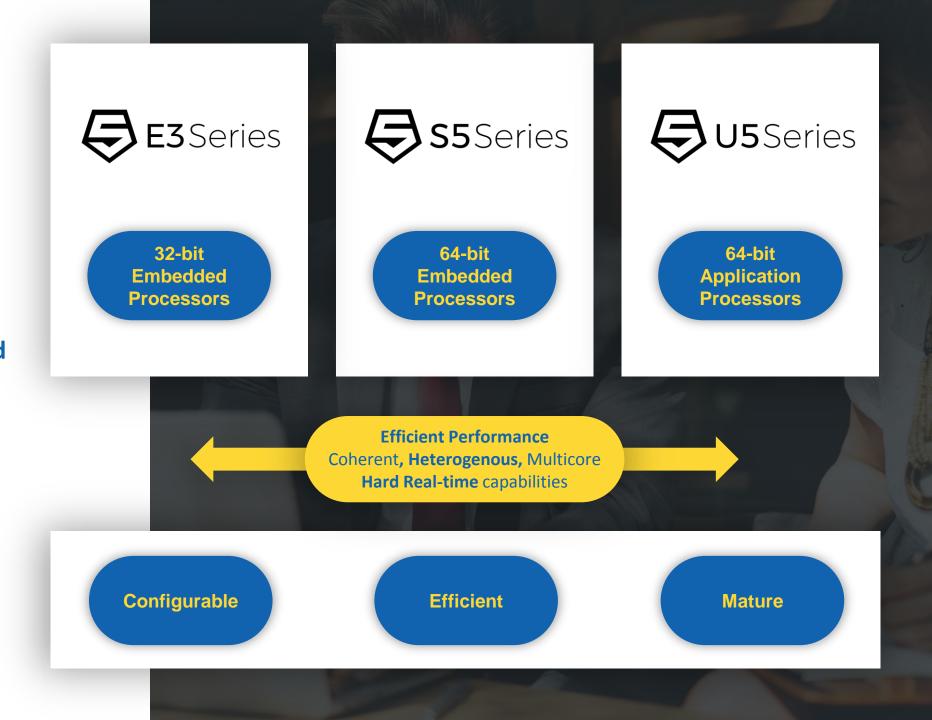

## SiFive Core IP 3 and 5 series:

The world's most deployed RISC-V processor IP

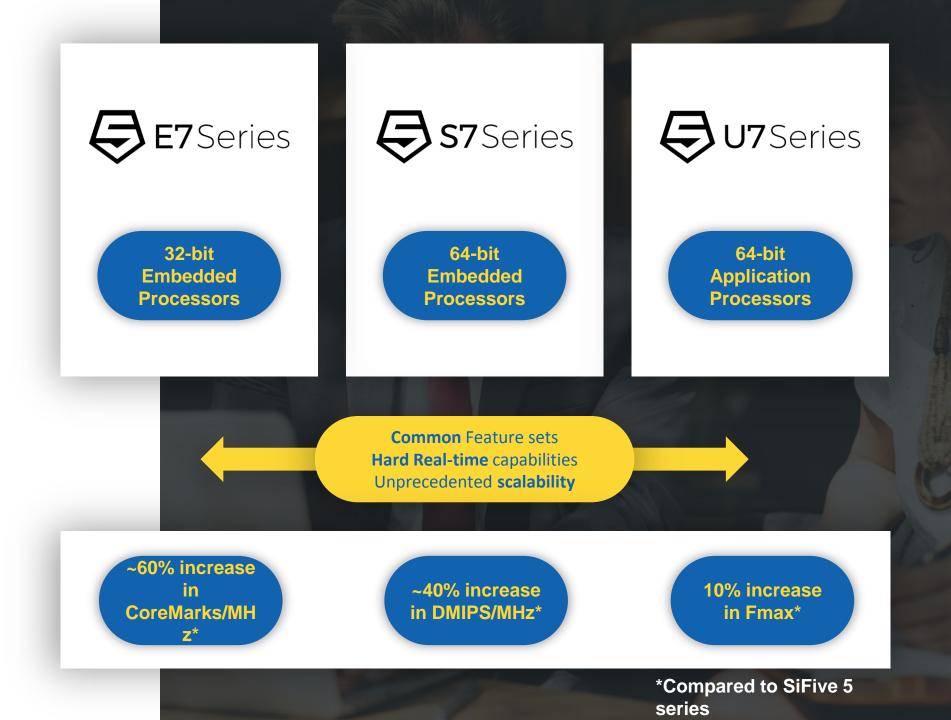

## SiFive Core IP 7 series:

The **highest performance** commercial **RISC-V** processor IP

# SiFive 7 Series Embedded Intelligence Everywhere

Scalable throughput provided by 8+1 cores per cluster

Extensible design via custom instructions

Configurable memory architecture for application specific tuning

U7Series Core Core PLIC PMP Debug I\$ w/ECC DTIM w/ECC D\$ w/ECC **Bus Matrix** Peripheral Port L2 Cache with ECC System Port Front Port **Memory Port** TileLink or AMBA

**Enhanced determinism** for hard real-time constraints

Functional safety provided by in-built fault tolerance mechanisms

A **single** pre-integrated and verified deliverable

Tightly integrated memory for low latency access

**64-bit addressability** for real time latency sensitive applications

Mixed-precision arithmetic for efficient compute of ML workloads

Cache lock capability for missioncritical computing

In-cluster coherent heterogenous combination of real-time and application processors

## Storage

Coherent in-cluster combination of application processors and real-time processors

Configurable memory maps and coherent accelerator ports for tightly coupling storage specific accelerators

**Optional FPU** for applications which don't need floating point capability

Deterministic mode for FAST DATA applications with hard real-time constraints

Tightly integrated memories and Cache lock capability for critical real time workloads

Storage, ML, Cryptography specific custom instructions

**64-bit real-time addressability** for **BIG DATA** applications

### 5G/Networking

Complex arithmetic capability for accelerating baseband functions

In-cluster coherence of application and real-time processor enables 5G latency (<1ms) requirements

High bandwidth accelerator ports for enabling intelligent offload processing

Hard real-time capabilities for scheduling baseband protocol layers

Configurable memory maps for optimizing QoS

High throughput processing for next gen 5G stacks

Tightly Integrated Memories and Cache lock capability for critical real time workloads

**AR/VR/Sensor Fusion**

Low Latency peripheral access and coherent accelerator port

Combine with SiFive 2, 3 or 5 series for designs with tight power constraints

Coherent in-cluster combination of application processors with real time processors

Workload specific customizations (AR/VR/MR/CV)

Simple caching hierarchy for ease of application optimization

Mixed precision arithmetic for accelerating machine learning compute

#### **SiFive** Recently announced products

**Wearable Al**

Rapid adoption of SiFive Core IP from the Edge to the Core

### Silicon verified. Market proven.

The most advanced configurable core IP and silicon solutions from the inventors of RISC-V.

Microcontrollers - Embedded - Linux - Multicore

- Networking Storage Computing Al

- Industrial IoT Consumer Automotive

www.sifive.com